МОП-транзистор является наиболее фундаментальным элементом в крупномасштабных интегральных схемах. Эти транзисторы обычно делятся на два типа PMOS и NMOS. Комбинация транзисторов NMOS и PMOS известна как КМОП-транзистор . Разные логические ворота и другие реализованные цифровые логические устройства должны иметь логику PMOS. Эта технология недорогая и имеет хорошую устойчивость к помехам. В этой статье обсуждается один из типов МОП-транзисторов, такой как PMOS-транзистор.

Что такое PMOS-транзистор?

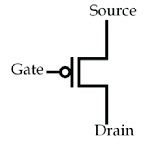

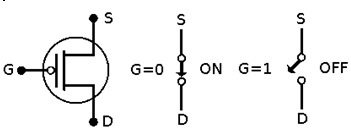

PMOS-транзистор или металлооксид-полупроводник с P-каналом представляет собой тип транзистора, в котором примеси p-типа используются в области канала или затвора. Этот транзистор является полной противоположностью NMOS-транзистора. Эти транзисторы имеют три основных вывода; исток, затвор и сток, где исток транзистора выполнен с подложкой p-типа, а вывод стока — с подложкой n-типа. В этом транзисторе носители заряда, такие как дырки, отвечают за проводимость тока. Символы транзисторов PMOS показаны ниже.

Как работает транзистор PMOS?

Работа транзистора p-типа совершенно противоположна транзистору n-типа. Этот транзистор образует разомкнутую цепь всякий раз, когда он получает незначительное напряжение, что означает отсутствие потока электричества от клеммы затвора (G) к истоку (S). Точно так же этот транзистор образует замкнутую цепь, когда на него подается напряжение около 0 вольт, что означает, что ток течет от вывода затвора (G) к стоку (D).

Этот пузырь также известен как инверсионный пузырь. Таким образом, основная функция этого круга — инвертировать значение входного напряжения. Если клемма затвора обеспечивает напряжение 1, то этот инвертор изменит его на ноль и будет соответствующим образом управлять схемой. Таким образом, функция транзистора PMOS и транзистора NMOS совершенно противоположна. Как только мы объединим их в единую схему МОП, она станет схемой КМОП (комплементарный металл-оксид-полупроводник).

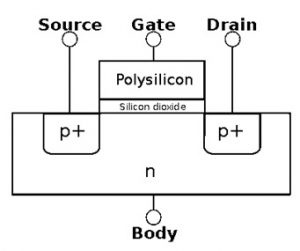

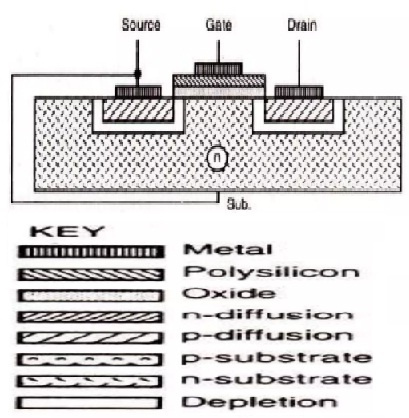

Поперечное сечение транзистора PMOS

Поперечное сечение транзистора PMOS показано ниже. Транзистор pMOS построен с корпусом n-типа, включающим две полупроводниковые области p-типа, которые примыкают к затвору. Этот транзистор имеет управляющий затвор, как показано на схеме, который управляет потоком электронов между двумя выводами, такими как исток и сток. В pMOS-транзисторе корпус удерживается при положительном напряжении. Как только клемма затвора положительна, клеммы истока и стока смещены в обратном направлении. Как только это произойдет, ток перестанет течь, поэтому транзистор будет выключен.

Как только напряжение питания на клемме затвора снижается, носители положительного заряда будут притягиваться к нижней части интерфейса Si-SiO2. Всякий раз, когда напряжение становится достаточно низким, канал инвертируется и создает проводящий путь от терминала истока к стоку, позволяя течь току.

Всякий раз, когда эти транзисторы имеют дело с цифровой логикой, они обычно имеют два разных значения, например 1 и 0 (ВКЛ и ВЫКЛ). Положительное напряжение транзистора известно как VDD, которое представляет собой высокое логическое значение (1) в цифровых схемах. Уровни напряжения VDD в Логика ТТЛ обычно были около 5В. В настоящее время транзисторы фактически не могут выдерживать такие высокие напряжения, потому что они обычно находятся в диапазоне от 1,5 до 3,3 В. Низкое напряжение часто называют GND или VSS. Таким образом, VSS означает логический «0», и он также обычно устанавливается на 0 В.

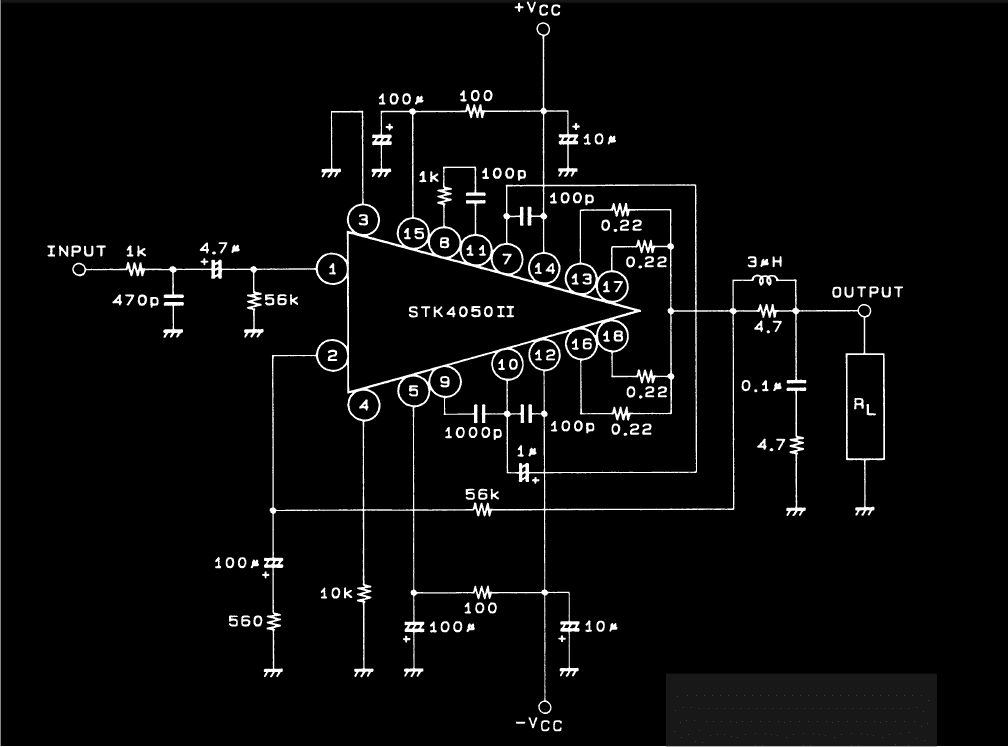

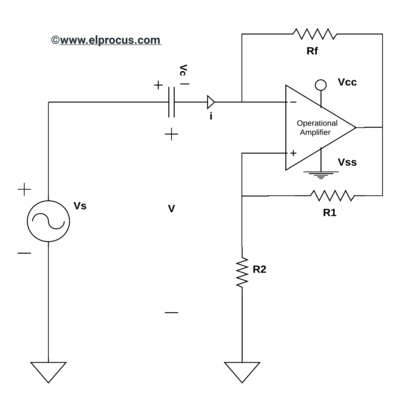

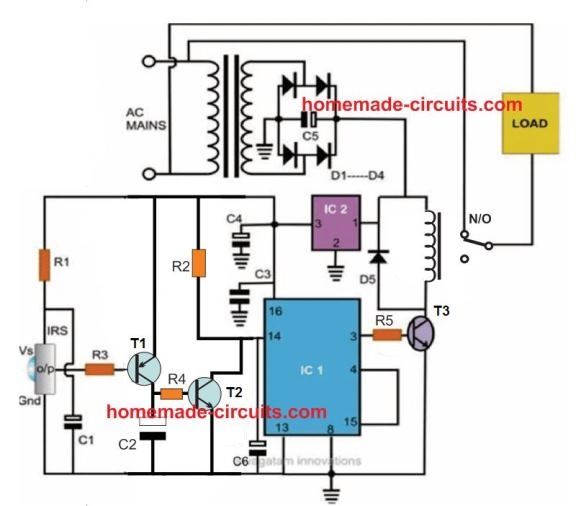

Схема транзистора PMOS

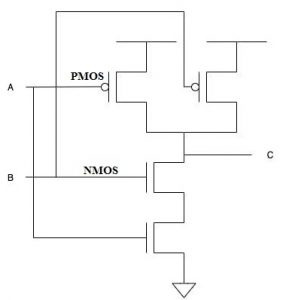

Ниже показана конструкция затвора И-НЕ с использованием транзистора PMOS и транзистора NMOS. Как правило, вентиль И-НЕ в цифровой электронике представляет собой логический вентиль, который также называют вентилем НЕ-И. На выходе этого вентиля низкий уровень (0), только если на двух входах высокий уровень (1), а его выход является дополнением к вентилю И. Если какой-либо из двух входов НИЗКИЙ (0), то он дает высокие выходные результаты.

В приведенной ниже логической схеме, если вход A равен 0, а B равен 0, то вход pMOS выдаст «1», а вход nMOS выдаст «0». Таким образом, этот логический элемент генерирует логическую «1», потому что он подключен к источнику по замкнутой цепи и отсоединен от GND через разомкнутую цепь.

Когда A равно «0», а B» равно «1», тогда вход pMOS будет генерировать «1», а вход NMOS будет генерировать «0». Таким образом, этот вентиль создаст логическую единицу, потому что он подключен к истоку через замкнутую цепь и отсоединен от GND разомкнутой цепью. Когда A равно «1», а B равно «0», тогда вход «B» pMOS будет генерировать высокий выходной сигнал (1), а вход «B» NMOS будет генерировать низкий выходной сигнал (0). Таким образом, этот логический элемент будет генерировать логическую 1, потому что он подключен к источнику через замкнутую цепь и отсоединен от GND разомкнутой цепью.

Когда A равно «1» и B равно «1», тогда ввод «pMOS» будет давать ноль, а ввод «nMOS» будет генерировать «1». Следовательно, мы также должны проверить вход B pMOS и nMOS. Вход B pMOS будет генерировать «0», а вход B nMOS будет генерировать «1». Таким образом, этот логический элемент будет генерировать логический «0», потому что он отсоединен от источника разомкнутой цепью и подключен к GND через замкнутую цепь.

Таблица истинности

Таблица истинности приведенной выше логической схемы приведена ниже.

|

А |

Б |

С |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

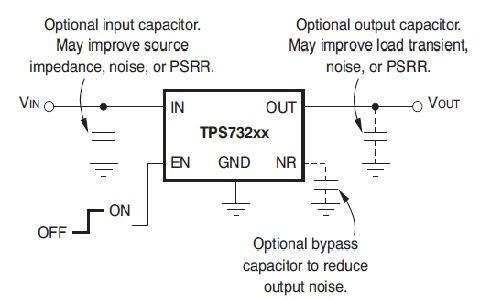

Пороговое напряжение транзистора PMOS обычно составляет «Vgs», что необходимо для создания канала, известного как инверсия канала. В транзисторе PMOS подложка и клеммы истока просто подключены к «Vdd». Если мы начнем уменьшать напряжение по отношению к клемме истока на клемме затвора от Vdd до точки, где вы заметите инверсию канала, в этой позиции, если вы проанализируете Vgs и источник, находящиеся под высоким потенциалом, вы получите отрицательное значение. Итак, транзистор PMOS имеет отрицательное значение Vth.

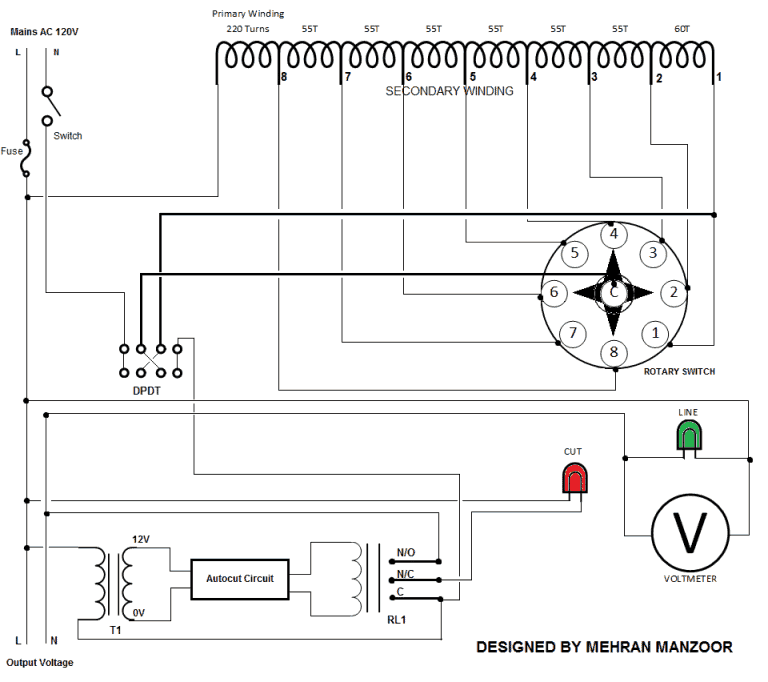

Процесс изготовления ПМОП

Шаги, связанные с изготовлением транзисторов PMOS, обсуждаются ниже.

Шаг 1:

Тонкий слой кремниевой пластины превращается в материал N-типа путем простого легирования фосфорным материалом.

Шаг 2:

Толстый слой диоксида кремния (Sio2) выращен на полной подложке р-типа.

Шаг 3:

Теперь поверхность покрыта фоторезистом поверх толстого слоя диоксида кремния.

Шаг 4:

После этого этот слой просто подвергается воздействию УФ-света через маску, определяющую те области, в которые должна происходить диффузия вместе с транзисторными каналами.

Шаг 5:

Эти области вытравливаются вместе с нижележащим диоксидом кремния, так что поверхность пластины открывается в пределах окна, определяемого маской.

Шаг 6:

Оставшийся фоторезист отделяют и наращивают тонкий слой Sio2, как правило, толщиной 0,1 микрометра по всей поверхности чипа. После этого поверх него помещают поликремний, чтобы сформировать структуру затвора. Фоторезист помещается по всему слою поликремния и экспонирует УФ-свет через маску2.

Шаг 7:

Диффузия достигается за счет нагрева пластины до максимальной температуры и пропускания газа с желаемыми примесями p-типа, такими как бор.

Шаг 8:

Выращивается диоксид кремния толщиной 1 микрометр и на него наносится фоторезист. Облучите ультрафиолетовым светом с маской 3 предпочтительные области затвора, истока и стока, которые протравлены, чтобы сделать контактные вырезы.

Шаг 9:

Теперь на его поверхность толщиной 1 микрометр наносится металл или алюминий. Опять же, по всему металлу выращивают фоторезистивный материал и подвергают воздействию УФ-света через маску4, которая вытравливается для формирования требуемой конструкции соединения. Окончательная структура PMOS показана ниже.

Характеристики транзистора PMOS

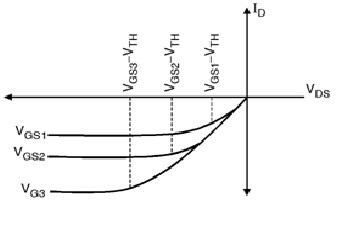

ВАХ PMOS-транзистора показаны ниже. Эти характеристики разделены на две области, чтобы получить взаимосвязь между током стока и истока (I DS), а также напряжениями на его клеммах, такими как линейная область и область насыщения.

В линейной области IDS будет линейно увеличиваться при увеличении VDS (напряжения сток-исток), тогда как в области насыщения IDS стабилен и не зависит от VDS. Основная взаимосвязь между ISD (током исток-сток) и напряжениями на его выводах определяется аналогичной процедурой для NMOS-транзистора. В этом случае единственным изменением будет то, что носители заряда, присутствующие в инверсионном слое, будут просто дырками. Когда дырки перемещаются от истока к стоку, ток тоже одинаков.

Таким образом, в текущем уравнении появляется отрицательный знак. Кроме того, все приложенные смещения на выводах устройства отрицательны. Итак, ID транзистора PMOS – характеристики VDS показаны ниже.

Уравнение тока стока для транзистора PMOS в линейной области задается как:

ID = – т.п. Кокса

Аналогично, уравнение тока стока для транзистора PMOS в области насыщения задается как:

ID = – mp Cox (VSG – | V TH |p )^2

Где «mp» — подвижность дыры, а «|VTH| p’ — пороговое напряжение транзистора PMOS.

В приведенном выше уравнении отрицательный знак будет означать, что ID( ток стока ) течет из стока (D) в исток (S), тогда как дырки текут в противоположном направлении. Когда подвижность дырки низка по сравнению с подвижностью электронов, PMOS-транзисторы страдают из-за возможности слаботочного привода.

Таким образом, это все, что касается обзора PMOS-транзистора или mos-транзистора p-типа — изготовления, схемы и его работы. ПМОС транзисторы предназначены с p-источником, n-подложкой и стоком. Носителями заряда PMOS являются дырки. Этот транзистор открывается, когда на клемму затвора подается низкое напряжение. Устройства на основе PMOS менее подвержены помехам по сравнению с устройствами NMOS. Эти транзисторы могут использоваться в качестве резисторов, управляемых напряжением, активных нагрузок, токовых зеркал, трансимпедансных усилителей, а также использоваться в переключателях и усилителях напряжения. Вот вопрос к вам, что такое NMOS-транзистор?