ECL (логика с эмиттерной связью) была впервые изобретена в IBM в августе 1956 года Хэнноном С. Юрком. Эта логика также известна как логика текущего режима, используемая в компьютерах IBM 7090 и 7094. Семейство ECL очень быстрое по сравнению с цифровая логика семьи. Как правило, это логическое семейство обеспечивает задержку распространения менее 1 нс. Это логическое семейство на основе транзисторов с биполярным переходом. Это самая быстрая схема из семейства логических, доступная для разработки обычной логической системы. В этой статье обсуждается обзор логическая схема с эмиттерной связью , работа с приложениями.

Что такое эмиттерно-связанная логика?

Эмиттерно-связанная логика является лучшей БЮТ логическое семейство, используемое в традиционной логической системе. Иногда ее также называют логикой текущего режима, которая представляет собой очень высокоскоростную цифровую технологию. Как правило, ECL считается самой быстрой логической ИС, где она достигает своей высокой скорости работы за счет использования очень небольшого колебания напряжения, а также избегая входа транзисторов в область насыщения.

Реализация ECL использует положительное напряжение питания, известное как PECL или ECL с положительной ссылкой. В ранних ECL-затворах используется отрицательное напряжение питания из-за помехозащищенности. После этого ECL с положительной ссылкой стал очень известен благодаря своим более совместимым логическим уровням по сравнению с логическими семействами TTL.

Логика с эмиттерной связью рассеивает огромное количество статической мощности, однако ее общее потребление тока низкое по сравнению с КМОП на высоких частотах. Таким образом, ECL в основном полезен в схемах распределения тактовых импульсов и высокочастотных приложениях.

Эмиттерно-связанные логические функции

Возможности ECL позволяют использовать их во многих высокопроизводительных приложениях.

- ECL обеспечивает два выхода, которые всегда дополняют друг друга, потому что работа схемы основана на дифференциальном усилителе.

- Это семейство логики в основном подходит для монолитных методов изготовления, поскольку логические уровни являются функцией отношения резисторов.

- Устройства семейства ECL генерируют правильный и дополнительный выходной сигнал предлагаемой функции без использования каких-либо внешних инверторов. Следовательно, это уменьшает количество пакетов и требования к мощности, а также уменьшает проблемы, возникающие из-за временных задержек.

- Устройства ECL в конструкции дифференциального усилителя обеспечивают большую гибкость характеристик, поэтому схемы ECL позволяют использовать как цифровые, так и линейные схемы.

- Конструкция затвора ECL обычно имеет высокий и низкий входной импеданс, что чрезвычайно способствует достижению большого разветвления, а также возможности управления.

- Устройства ECL генерируют постоянный потребляемый ток в источнике питания, чтобы упростить конструкцию источника питания.

- Устройства ЭХЛ, включающие выходы с открытым эмиттером, просто позволяют включать в них мощность привода линии передачи.

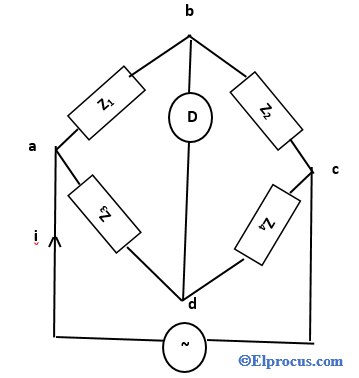

Логическая схема с эмиттерной связью

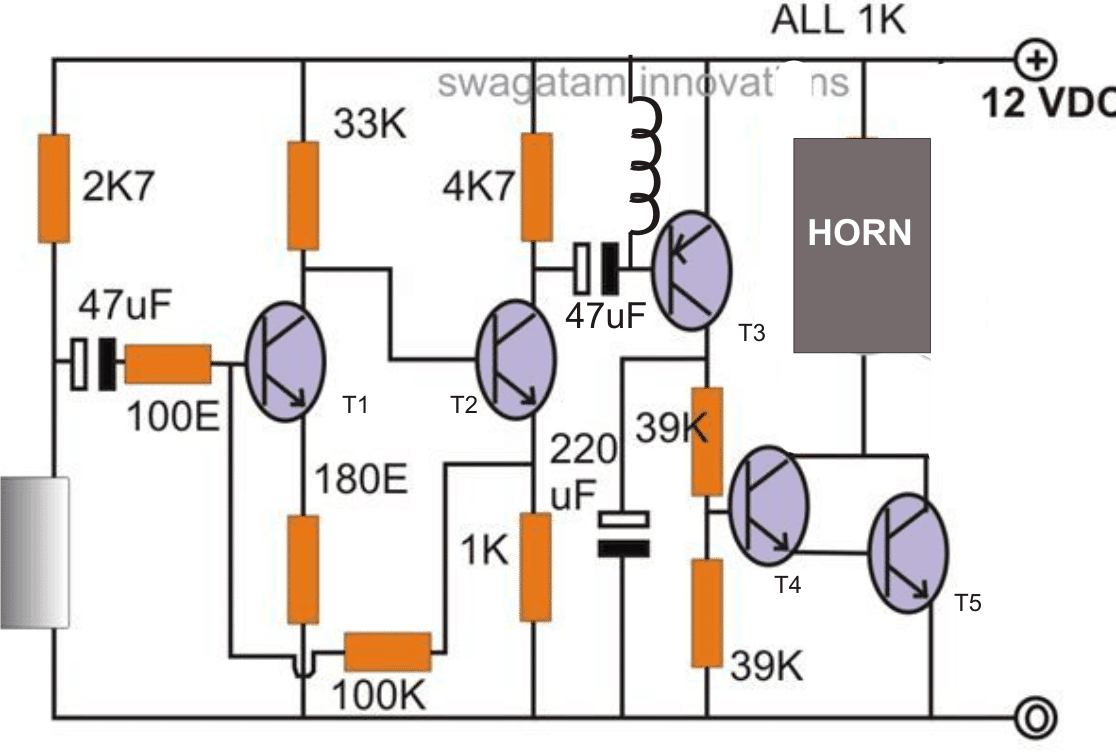

Ниже показана логическая схема инвертора с эмиттерной связью, состоящая из резисторов и транзисторов. В этой схеме выводы эмиттера двух транзисторов просто подключены к токоограничивающему сопротивлению RE, которое используется для предотвращения насыщения транзистора. Здесь выход транзистора берется с клеммы коллектора, а не с клеммы эмиттера. Эта схема имеет два выхода Vout (инвертирующий выход) и Vout2 (неинвертирующий выход) и входную клемму, такую как Vin, на которую подается высокий или низкий входной сигнал. +Vcc = 5В.

Как работает эмиттерно-связанная логика?

Работа логики с эмиттерной связью заключается в том, что всякий раз, когда на схему ECL подается ВЫСОКИЙ вход, транзистор Q1 включается, а транзистор Q2 выключается, но транзистор Q1 не насыщается. Таким образом, это поднимет выход VOUT2 до ВЫСОКОГО, а значение выхода VOUT1 будет НИЗКИМ из-за падения на резисторе R1.

Точно так же, когда значение VIN, заданное для ECL, НИЗКОЕ, тогда транзистор Q1 ВЫКЛ., а транзистор Q2 ВКЛ. Таким образом, транзистор Q2 не перейдет в насыщение. Таким образом, выход VOUT1 будет иметь ВЫСОКОЕ значение, а выходное значение VOUT2 будет низким из-за падения сопротивления R2.

Давайте посмотрим, как транзисторы Q1 и Q2 включаются и выключаются при подаче напряжения.

Два транзистора, такие как Q1 и Q2 в этой схеме, соединены как дифференциальный усилитель резистором с общим эмиттером.

Источники напряжения для этой примерной схемы: VCC = 5,0, VBB = 4,0 и VEE = 0 В. Входные значения ВЫСОКОГО и НИЗКОГО уровней просто определяются как 4,4 В и 3,6 В. На самом деле, эта схема генерирует НИЗКИЙ и ВЫСОКИЙ уровни выходного сигнала, которые на 0,6 В выше; однако это корректируется в реальных схемах ECL.

Как только Vin становится ВЫСОКИМ, транзистор Q1 включается, но не насыщается, а транзистор Q2 выключается. Таким образом, выходное напряжение, такое как VOUT2, увеличивается до 5 В через резистор R2, и можно показать, что падение напряжения на резисторе R1 составляет около 0,8 В, поэтому VOUT1 = 4,2 В (НИЗКИЙ). Кроме того, VE = VOUT1 – VQ1 => 4,2 В – 0,4 В = 3,8 В, поскольку транзистор Q1 полностью открыт.

Когда Vin становится НИЗКИМ, транзистор Q2 включается, но не насыщается, а транзистор Q1 выключается. Таким образом, VOUT1 подтягивается до 5,0 В с помощью резистора R1, и можно показать, что VOUT2 составляет 4,2 В. Также VE => VOUT2 – VQ2 => 4,2 В – 0,8 В => 3,4 В, когда транзистор Q2 включен.

В ECL два транзистора никогда не находятся в состоянии насыщения, т.к. Колебания входного / выходного напряжения довольно малы, например, 0,8 В. и входное сопротивление высокое, а выходное сопротивление низкое. Это помогает ECL работать быстрее с меньшим временем задержки распространения.

Логическая схема логического элемента ИЛИ/НЕ с двумя входами, связанная с эмиттером

Ниже показана схема логического элемента ИЛИ/НЕ, связанная с двумя входами-эмиттерами. Эта схема разработана путем модификации приведенной выше схемы инвертора. Модификация заключается в добавлении дополнительного транзистора на входе.

Работа этой схемы очень проста. Когда входы, подаваемые на оба транзистора Q1 и Q2, имеют низкий уровень, выход 1 (Vout1) устанавливается в ВЫСОКОЕ значение. Итак, этот Vout1 соответствует выходу вентиля ИЛИ-НЕ.

Одновременно, если транзистор Q3 будет включен, то второй выход (Vout2) станет ВЫСОКИМ. Итак, этот выход Vou2 соответствует выходу вентиля ИЛИ.

Таким же образом, если оба входа транзисторов Q1 и Q2 имеют ВЫСОКИЙ уровень, то он включит транзисторы Q1 и Q2 и обеспечит низкий уровень на выходе VOUT1.

Если транзистор Q3 выключен во время этой операции, то он обеспечит высокий выходной сигнал на клемме VOUT2. Итак, таблица истинности для вентиля ИЛИ/НЕ приведена ниже.

|

Входы |

Входы | ИЛИ ЖЕ |

НИ |

|

А |

Б | Д | Д |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Характеристики эмиттерно-связанной логики

Характеристики ECL включают следующее.

- По сравнению с TTL, ECL имеет более быстрое время распространения от 0,5 до 2 нс. Но рассеиваемая мощность логики с эмиттерной связью выше по сравнению с ТТЛ, например 30 мВт.

- Напряжения ввода-вывода ECL имеют небольшой размах, например 0,8.

- Входной импеданс ECL высок, а выходное сопротивление низкое; следовательно, транзистор очень быстро меняет свое состояние.

- Емкость разветвления ECL высока, а задержки затвора низки.

- Логика o/p ECL изменяется с НИЗКОГО на ВЫСОКОЕ состояние, но уровни напряжения для этих состояний будут варьироваться между TTL и EC.

- Помехоустойчивость ЭХЛ 0,4В.

Преимущества и недостатки

преимущества эмиттерно-связанной логики обсуждаются ниже.

- Разветвление ECL составляет 25, что лучше по сравнению с TTL и меньше по сравнению с CMOS.

- Среднее время задержки распространения ECL составляет от 1 до 4 нс, что лучше по сравнению с CMOS и

- ТТЛ. Таким образом, это называется самым быстрым логическим семейством.

- Когда биполярные транзисторы в эмиттере соединены логические ворота работают в активной области, то имеют максимальное быстродействие по сравнению со всеми семействами логики.

- Вентиляторы ECL генерируют дополнительные выходные данные.

- Токовых пиков коммутации в проводах блока питания нет.

- Выходы могут быть соединены вместе для обеспечения функции проводного ИЛИ.

- Параметры ECL не сильно меняются в зависимости от температуры.

- Нет. функций, доступных из единственного чипа, велико.

недостатки эмиттерно-связанной логики обсуждаются ниже.

- Он имеет чрезвычайно меньший запас по шуму, т. е. ±200 мВ.

- Рассеиваемая мощность высока по сравнению с другими логическими вентилями.

- Для взаимодействия с другими логическими семействами необходимы переключатели уровней.

- Разветвитель ограничивает емкостную нагрузку.

- По сравнению с время жизни , ворота ECL стоят дорого.

- По сравнению с CMOS и TTL помехоустойчивость ECL хуже.

Приложения

Приложения логики с эмиттерной связью включают следующее.

- Логика, связанная с эмиттером, используется в качестве технологии логики и интерфейса в высокоскоростных устройствах связи, таких как интерфейсы оптоволоконных приемопередатчиков, сети Ethernet и ATM (асинхронный режим передачи).

- ECL — это логическое семейство, основанное на BJT, где его высокоскоростная работа может быть достигнута за счет использования относительно небольшого размаха напряжения и предотвращения перехода транзисторов в область насыщения.

- ECL используется при создании схем ASLT в IBM 360/91.

- ECL позволяет избежать использования многослойных транзисторов за счет использования несимметричного смещения i/p и положительной обратной связи между первичным и вторичным транзисторами для достижения функции инвертора.

- ECL используется в чрезвычайно быстродействующей электронике.

Таким образом, это обзор эмиттерно-связанной логики или ECL - схема, работа, функции, характеристики и приложения. ECL — это очень быстрое семейство логики, основанное на BJT, по сравнению с другими семействами цифровой логики. Он достигает максимальной скорости работы, используя небольшой размах напряжения и избегая перехода транзисторов в область насыщения. Это семейство логики обеспечивает невероятную задержку распространения 1 нс, а в последних семействах ECL эта задержка уменьшена. Вот вопрос к вам, какое альтернативное название для ECL?